| OP Amp 강의 로드맵 | ||||

| OP Amp 기초 (연산증폭기 기초) |

→ | Ideal OP Amp (이상적인 연산증폭기) |

→ | 전압 팔로워 (Voltage Follower) |

| 반전 / 비반전증폭기 (Inverting / Non Inverting Amplifier) |

||||

| 차동증폭기 (Differential Amplifier) |

||||

| 가산증폭기 (Summing Amplifier) |

||||

| 비교기 (Comparator) |

||||

시작하기 전에…

안녕하세요 공대생의 오아시스입니다. ^^

이번 시간에 배울 내용 역시 OP Amp 응용회로 중 하나인 ‘가산증폭기(Summing Amplifier)’가 되겠습니다.

반복되는 내용에 지겨우시겠지만 핵심만 짚고 빠르게 넘어갈테니 좀만 참아주세요 ㅎㅎ.

가산증폭기(Summing Amplifier) 분석

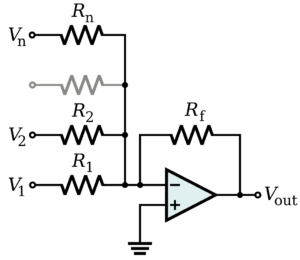

특이하게 – 입력단자 하나에서 n개의 입력전압을 받아들이네요.

근데 그 점을 제외하면 달리 특별한건 없습니다.

Negative Feedback에 저항이 하나 달려있고… + 입력단자에는 아무것도 없이 GND만 연결되어있네요.

생긴 것만 봐서는 반전증폭기 돌연변이인데… 기능은 어떨지 한번 분석해봅시다.

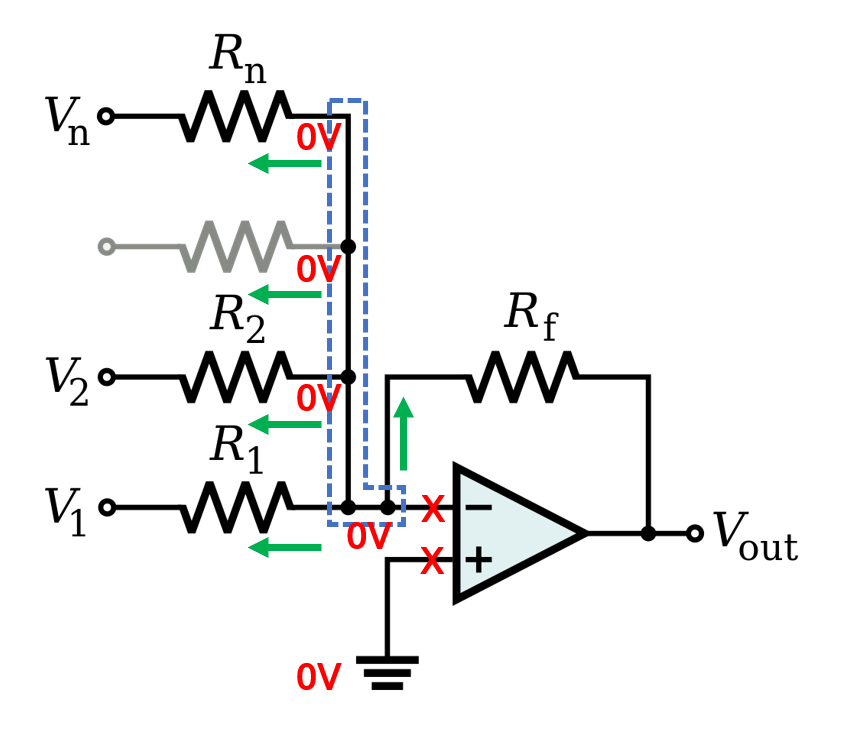

우선 Ideal OP Amp의 조건에 의해 + 입력단자 전압이 0V이므로 Negative Feedback 분기점과 모든 입력전압 분기점은 0V의 전압을 가집니다.

이때 파란 점선으로 표시해둔 것처럼 모든 분기점을 한 점으로 생각하여 KCL 식을 세워주면 되는데 여기에 대한 자세한 설명은 생략하겠습니다.

(OP Amp를 공부하시는 분이라면 기본적인 전기회로는 볼 줄 알 것이라고 믿습니다. ^^)

\mathrm{-\frac{V_{out}}{R_f}=\frac{V_1}{R_1}+\frac{V_2}{R_2}+\cdot\cdot\cdot+\frac{V_n}{R_n}}

대충 출력전압이 n개 입력전압의 합과 관계있어보이는 식은 나왔지만 아직 뭔가 미묘하네요…

여기서 모든 저항의 크기가 같다는 조건을 추가해볼까요?

\mathrm{V_{out}=-(V_1+V_2+\cdot\cdot\cdot+V_n)}

놀랍게도 출력전압은 입력전압의 합의 마이너스가 된다는 깔끔한 식이 나옵니다.

가산증폭기의 기능은 바로 이것입니다.

저항값을 적절히 조절하여 각 입력전압들의 특정 배수 합을 출력전압으로 만들 수 있는 것이죠.

저항값을 잘만 잡아주면 \mathrm{V_{out}=-(V_1/2+V_2/3+\cdot\cdot\cdot+V_n/7)} 같은 출력도 가능합니다.

다만 앞에 붙는 – 는 어쩔 수가 없습니다.

반전증폭기를 한번 더 이용하여 극성만 반대로 바꿔주거나 해야겠네요.

마치며…

이렇게 전압팔로워(Voltage Follower)부터 가산증폭기(Summing Amplifier)까지 대표적인 OP Amp 응용회로 설명이 모두 끝났습니다.

다음 시간에 비교기(Comparator)라는 놈을 다루긴 할 거지만 얘는 Negative Feedback도 없고 성질이 좀 다르니 노카운트로… ㅎㅎ

이전 강의를 다 듣고 오셨다는 가정 하에 진행했기 때문에 이 글이 저와의 첫 만남이신 분들은 중간중간 공백이 느껴지는 부분도 많았을 텐데 어떻게 잘 따라오셨을지 모르겠네요… ㅠㅠ

아무튼 부족한 글 읽어주셔서 정말 감사드립니다.

지금까지 공대생의 오아시스였습니다. ^^

개재밌어요 사랑합니다