| OP Amp 강의 로드맵 | ||||

| OP Amp 기초 (연산증폭기 기초) |

→ | Ideal OP Amp (이상적인 연산증폭기) |

→ | 전압 팔로워 (Voltage Follower) |

| 반전 / 비반전증폭기 (Inverting / Non Inverting Amplifier) |

||||

| 차동증폭기 (Differential Amplifier) |

||||

| 가산증폭기 (Summing Amplifier) |

||||

| 비교기 (Comparator) |

||||

시작하기 전에…

안녕하세요 공대생의 오아시스입니다. ^^

이번 시간에는 OP AMP (Operational Amplifier), 우리말로는 연산증폭기에 대해 알아보려고 하는데요.

이게 처음 배울 때 굉장히 어렵게 다가오는 개념들 중 하나입니다.

알고 보면 별거 아닌 놈이지만 가진 특징이 너무 많아 설명 순서가 뒤죽박죽이 되어버리기 쉽기 때문입니다.

가진 특징이 많은 만큼 전기회로에서 자주 모습을 보이는 놈이니까 이번 기회를 통해 OP AMP를 확실히 알아가시기 바랍니다 ㅎㅎ.

1. OP AMP, 연산증폭기의 정체

처음부터 OP AMP의 등가회로를 보여주고 여러가지 특징들을 설명드리면 OP AMP는 어려운 것이라고 선입견이 생겨버릴겁니다.

일단 따분한 이론은 치워두고 OP AMP, 연산증폭기의 정체에 대해 먼저 알아보도록 합시다.

우리말은 뒤에 오는 말이 단어의 본질을 나타냅니다.

황소개구리는 결국 개구리고, 감귤은 결국 귤인 것처럼요 ㅎㅎ.

그렇다면 연산증폭기는 뭘까요? 네 맞습니다. 증폭기입니다.

증폭기가 무언가를 증폭시켜주는 놈이라는 건 알겠는데… 여기서 말하는 OP AMP는 대체 무엇을 증폭시켜준다는 걸까요?

답은 ‘전압’ 입니다.

한마디로 OP AMP라는 것은 입력받은 전압을 증폭시켜 출력해주는 놈이라고 할 수 있습니다.

어때요, 어려울 것 없죠? ^^

이어지는 지식들을 받아들이기 위한 준비는 이 정도면 충분합니다.

부디 지금 이야기해드린 OP AMP의 ‘본질’을 새겨두시길 바랍니다.

2. OP AMP의 기호 및 요소

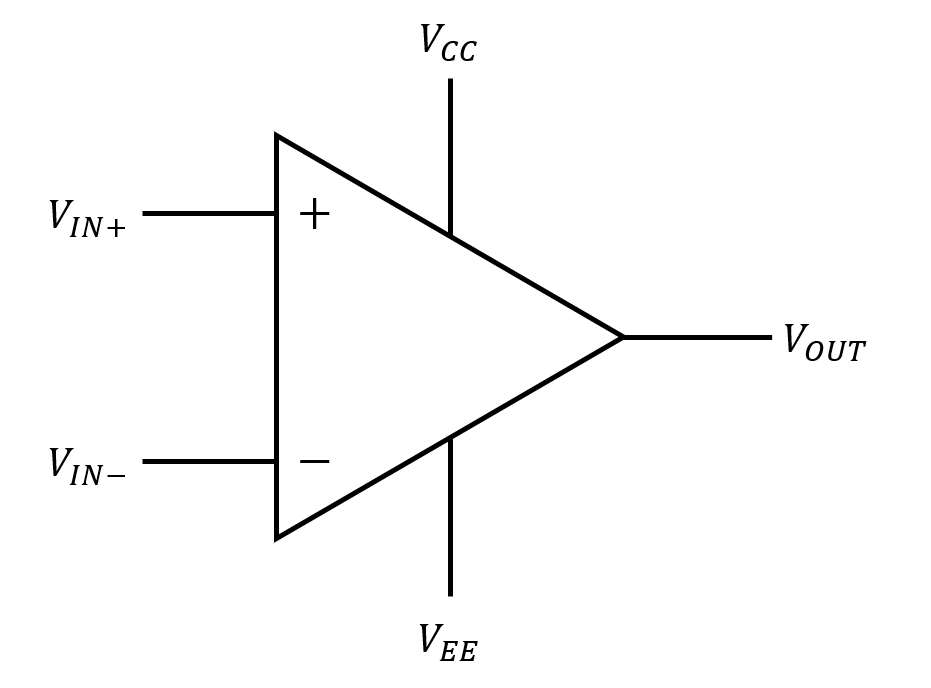

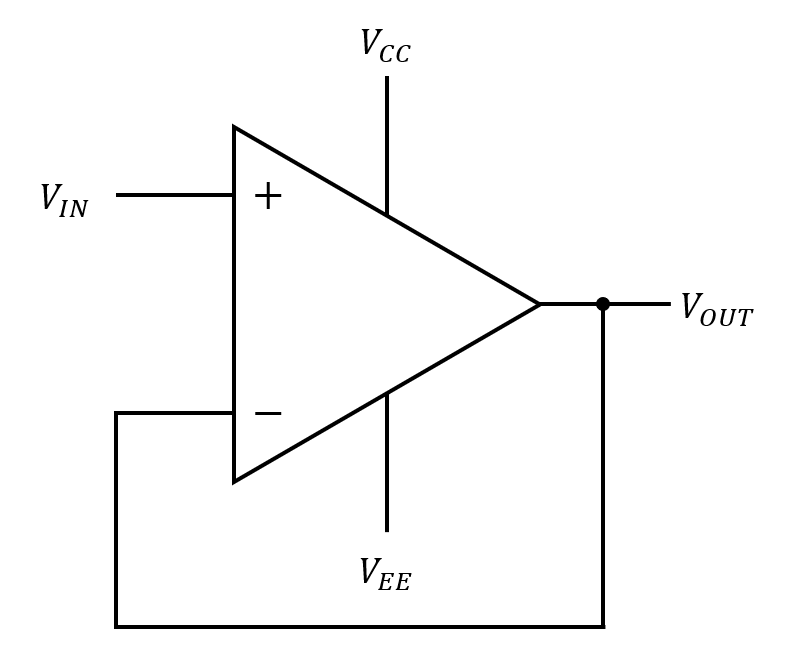

익숙치 않으시겠지만 전기회로에서는 OP AMP를 위와 같은 기호로 나타냅니다.

실제로는 여러가지 소자들이 복잡하게 얽혀있지만 필수 요소들만 간추려 단순하게 표현한 것입니다.

단순하다고는 해도… 알 수 없는 표현들이 많이 보이네요… ^^

그렇다고 겁먹을 필요는 없습니다. 우리는 이미 OP AMP가 뭐하는 놈인지 대충 알거든요 ㅎㅎ…

눈치빠른 분들은 이미 아시겠지만, OP AMP는 \mathrm{{V}_{IN}} 단자로부터 입력받은 전압을 증폭하여 \mathrm{{V}_{OUT}} 단자로 출력해줍니다.

이때 잘 보시면 IN 단자가 두 개 있는데 OP AMP는 둘 중 하나의 전압을 증폭시켜 주는 것이 아니라 두 단자에 걸린 전압값의 차이를 증폭시켜주는 것입니다.

+ 에 해당되는 IN 단자를 Non-Inverting Input(비반전입력) 단자, – 에 해당되는 IN 단자를 Inverting Input(반전입력) 단자라고도 하는데 굳이 무리해서 외울 필요는 없습니다.

이 글에서는 그냥 편하게 + 단자, – 단자라고 표현하겠습니다.

이렇게 되면 의문점이 한 가지 남습니다.

\mathrm{{V}_{CC}, {V}_{EE}} 는 어디에 쓰는 걸까요?

이 두 전압은 Bias Voltage 라고 하는데, OP AMP가 제대로 동작하기 위한 ‘전원’ 같은거라고 생각하시면 편합니다.

CC가 + 를, EE가 – 를 맡고있으며, 이것에 대해서는 또 재미있는 특징이 한 가지 있습니다.

바로 ‘포화 (Saturation)’ 입니다.

이 내용은 Gain(전압이득)과 함께 아래의 ‘OP AMP의 기능 및 특징’ 단계에서 설명드리겠습니다.

3. OP AMP의 기능 및 특징

3-1. Gain(전압이득)

OP AMP가 전압을 증폭시켜준다는 건 알겠는데, 얼마나 증폭시켜주는지에 대해서는 아직 설명드리지 않았습니다.

우선 Gain(전압이득)이라는 개념에 대해서 알아야합니다.

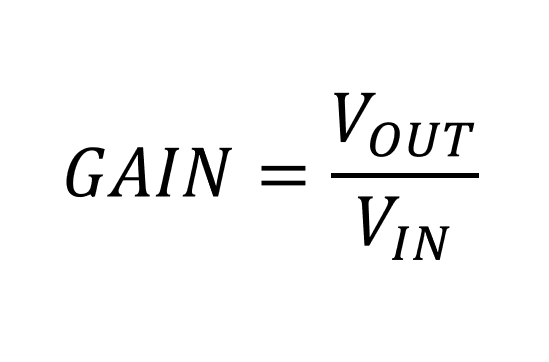

뭐 크게 어려운건 아닙니다. 단순히 출력이 입력의 몇 배가 되어 나왔는지를 나타내는 겁니다.

만약 2V를 넣었더니 6V가 되서 나오고, 3V를 넣었더니 9V가 되서 나온다면 그 OP AMP의 Gain은 3입니다.

따라서 Gain을 식으로 표현하면 다음과 같이 나타낼 수 있습니다.

3-2. Feedback

이제부터가 중요한데요, OP AMP의 Gain은 연결 상태에 따라 달라집니다.

당장은 무슨 소리인지 이해가 가지 않는 것이 당연합니다.

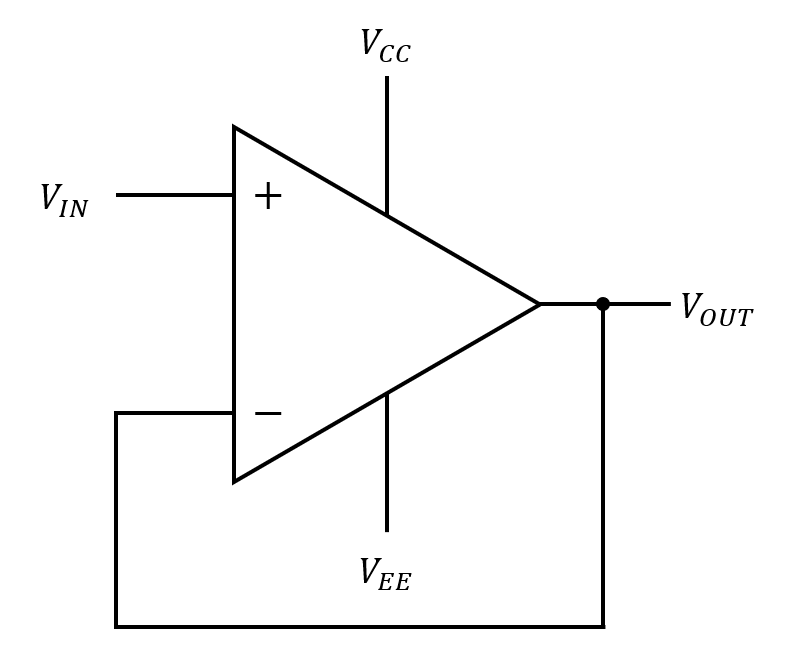

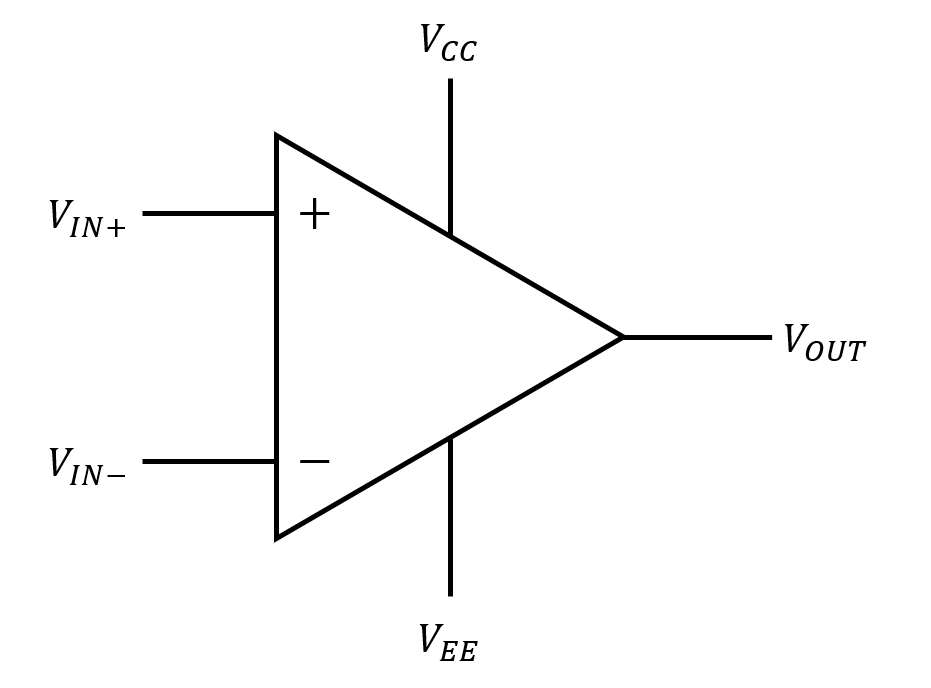

우선 아래 사진을 한번 보시죠.

회로가 이상하게 변했습니다.

이게 실제로 동작할지도 의문이 들고 대체 뭐가 어떻게 된건지 혼란스러우시겠지만 정상적인 반응이니 걱정하지 않으셔도 됩니다.

자 진정하시고… 우선 뭐가 달라졌는지 제대로 살펴보는 겁니다.

출력 단자에서 나오는 선이 다시 – 입력 단자로 들어가네요?

이런 식으로 출력이 다시 입력으로 들어가는 것을 Feedback이라고 하는데요.

– 입력단자로 들어가면 Negative Feedback, + 입력단자로 들어가면 Positive Feedback이라고 합니다.

이 경우 – 입력단자로 들어가니까 Negative Feedback이 되겠네요.

여기서 알아두셔야 할 중요한 사실이 있습니다.

Negative Feedback이 있을 때와 없을 때 OP AMP의 Gain은 천지차이라는 것입니다.

위에서 말씀드렸던 OP AMP의 Gain이 연결 상태에 따라 달라진다는 말은 이것을 의미합니다.

일단 이 사실은 그냥 받아들이셔야 합니다.

OP AMP의 특징이 워낙에 많다보니 처음부터 모든 것을 설명드릴 수는 없습니다.

깊게 생각하실 필요 없이 OP AMP에 대해 몇 가지 더 배우면 자연스레 이해할 수 있게 될 것이니 지금은 그냥 넘어가시기 바랍니다.

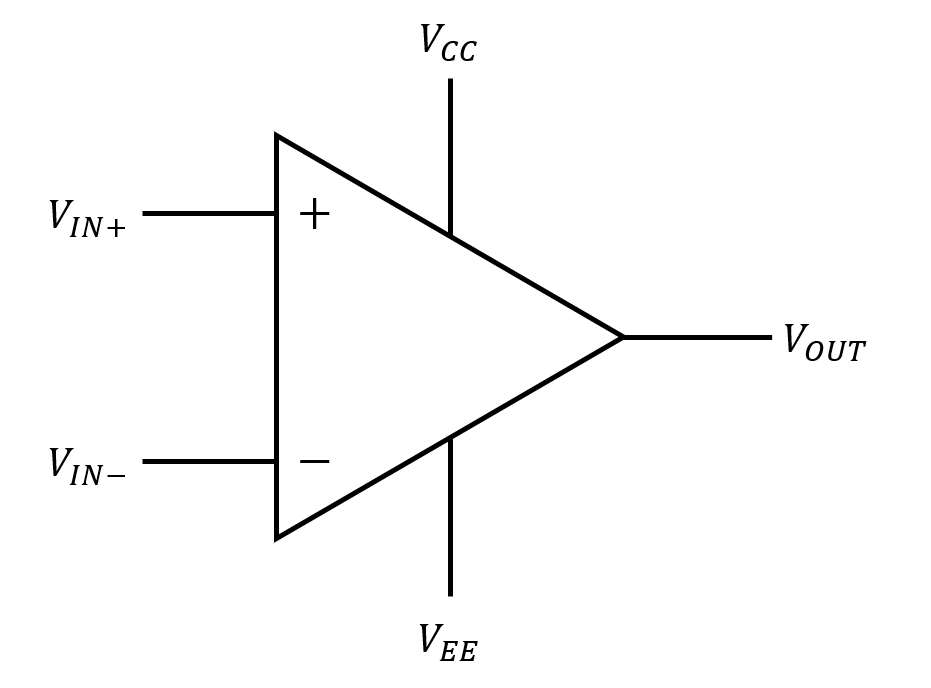

3-3. Open Loop Gain

가장 처음에 보여드렸던 어떠한 Feedback도 존재하지 않는 기본적인 상황입니다.

이상적인(Ideal) OP AMP는 이러한 상태에서 ∞의 Gain 값을 가져야하지만 실제로는 구현이 불가능하기 때문에 대부분의 실제 OP AMP들은 충분히 큰 값(수만~수십만)의 Gain을 가집니다.

그런데 아까 말씀드렸듯이 Negative Feedback이 있을 때와 없을 때 OP AMP의 Gain은 천지차이이기 때문에 두 경우에 차별을 둘 필요가 있었고, 그렇게 나온 것이 Open Loop Gain[ \mathrm{A_O} ]입니다.

위와 같은 상황, 즉 Feedback이 없는 구성에서의 Gain을 Open Loop Gain이라고 하며 보통 \mathrm{A_O}로 많이 표시합니다.

문제를 풀 때는 보통 Ideal OP AMP에 대해서만 다루게 되므로 Open Loop Gain이 무엇인지와 매우 큰 값을 가진다는 것만 알아두셔도 됩니다.

3-4. Negative Feedback을 쓰는 이유

그렇다면 Negative Feedback이 존재하는 경우는 어떻게 될까요?

지금 단계에서 구체적으로 말씀드릴 수는 없지만 Gain이 쓸만한 값이 됩니다.

Feedback이 없는 경우의 Gain, 즉 Open Loop Gain은 매우 큰 값을 가지기 때문에 미세한 입력도 뻥튀기가 되어 출력에 큰 영향을 미치게 됩니다.

그리고 2배, 3배 정도의 증폭만을 원하는데 Gain이 쓸데없이 크기만 하다면 원하는 출력값을 얻는 과정이 매우 힘들어집니다.

결국 Feedback이 없는 상태의 OP AMP는 Gain이 너무 크기 때문에 우리가 원하는 증폭기의 기능을 제대로 수행할 수 없는 것입니다.

이러한 문제를 해결해주는 것이 바로 Negative Feedback입니다.

믿기 어려우시겠지만 위 사진과 같은 형태를 갖춤으로써 Gain을 쓸만한 범위 내에 들어오게 할 수 있습니다.

이해가 되지 않는 것이 당연합니다.

차차 설명드릴테니 일단 지금은 그냥 그렇구나~ 하고 넘어가시길 바랍니다.

정리하자면 Negative Feedback은 Gain을 쓸만한 범위 내에 들어오게 함으로써 증폭기를 제어 가능한 상태로 만들기위해 사용되는 것입니다.

따라서 우리가 흔히 사용할법한 의미있는 증폭기능은 대부분 Negative Feedback을 통해 구현된다고 할 수 있습니다.

또한, 같은 Feedback이지만 Positive Feedback의 경우 너무 극단적으로 증폭되기 때문에 자주 사용되지 않습니다.

이 내용들은 이후 강의에서 더 자세히 다룰 예정입니다.

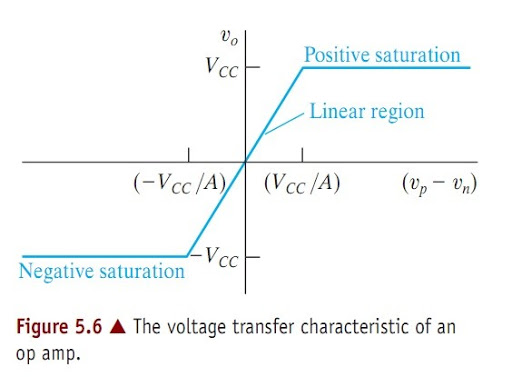

3-5. 포화(Saturation)

위에서 Open Loop Gain은 매우 큰 값을 가지기 때문에 Feedback이 없는 상황에서는 미세한 입력도 뻥튀기가 되어 출력에 큰 영향을 미치게 된다고 말씀드렸습니다.

그렇다면 만약 입력 전압을 충분히 크게 준다면 무지막지하게 큰 값의 전압을 출력해낼 수 있을까요?

이에 대한 답은 ‘아니오’ 입니다.

이유는 바로 OP AMP의 포화(Saturation)라는 특별한 성질 때문입니다.

출력전압은 어떤 상황이던간에 Bias Voltage \mathrm{{V}_{CC}} ~ \mathrm{{V}_{EE}} 범위를 벗어나지 못합니다.

(여기서 ‘어떤 상황이던간에’라는 말은 ‘Feedback이 있든 없든 상관없이’를 의미합니다.)

예를 들어 Open Loop Gain이 1000인 어떤 OP AMP가 있는데, Feedback이 없는 상황에서 + 입력단자와 – 입력단자의 전압차이가 3V가 되도록 입력을 주었다고 해봅시다.

이때 \mathrm{{V}_{CC}}에는 +15V, \mathrm{{V}_{EE}}에는 -15V의 전압이 인가되었다고 가정합니다.

단순 계산으로 따지면 출력 전압은 입력 전압의 1000배인 3000V가 되어야 할 것입니다.

하지만 Saturation에 의해 실제로는 15V가 출력됩니다.

범위를 벗어나지 못한다는 것은 이러한 것을 의미합니다.

Native Feedback의 경우도 예외는 아닙니다.

만약 계산을 통해 도출된 출력 전압이 \mathrm{{V}_{EE}} 아래로 내려간다면 \mathrm{{V}_{EE}}가 출력되고 \mathrm{{V}_{CC}} 위로 올라간다면 \mathrm{{V}_{CC}}가 출력됩니다.

Positive Feedback의 경우는 조금 특별하게 항상 Saturation된 결과만을 출력합니다.

\mathrm{{V}_{CC}}와 \mathrm{{V}_{EE}}의 중간값을 기준으로 조금이라도 크면 \mathrm{{V}_{CC}}를, 조금이라도 작으면 \mathrm{{V}_{EE}}를 출력합니다.

이러한 특징 때문에 특정 전압값보다 큰지 작은지를 판단하는 비교기(Comparator)로 이용된다는 것 정도만 알면 충분합니다.

4. OP AMP의 등가회로

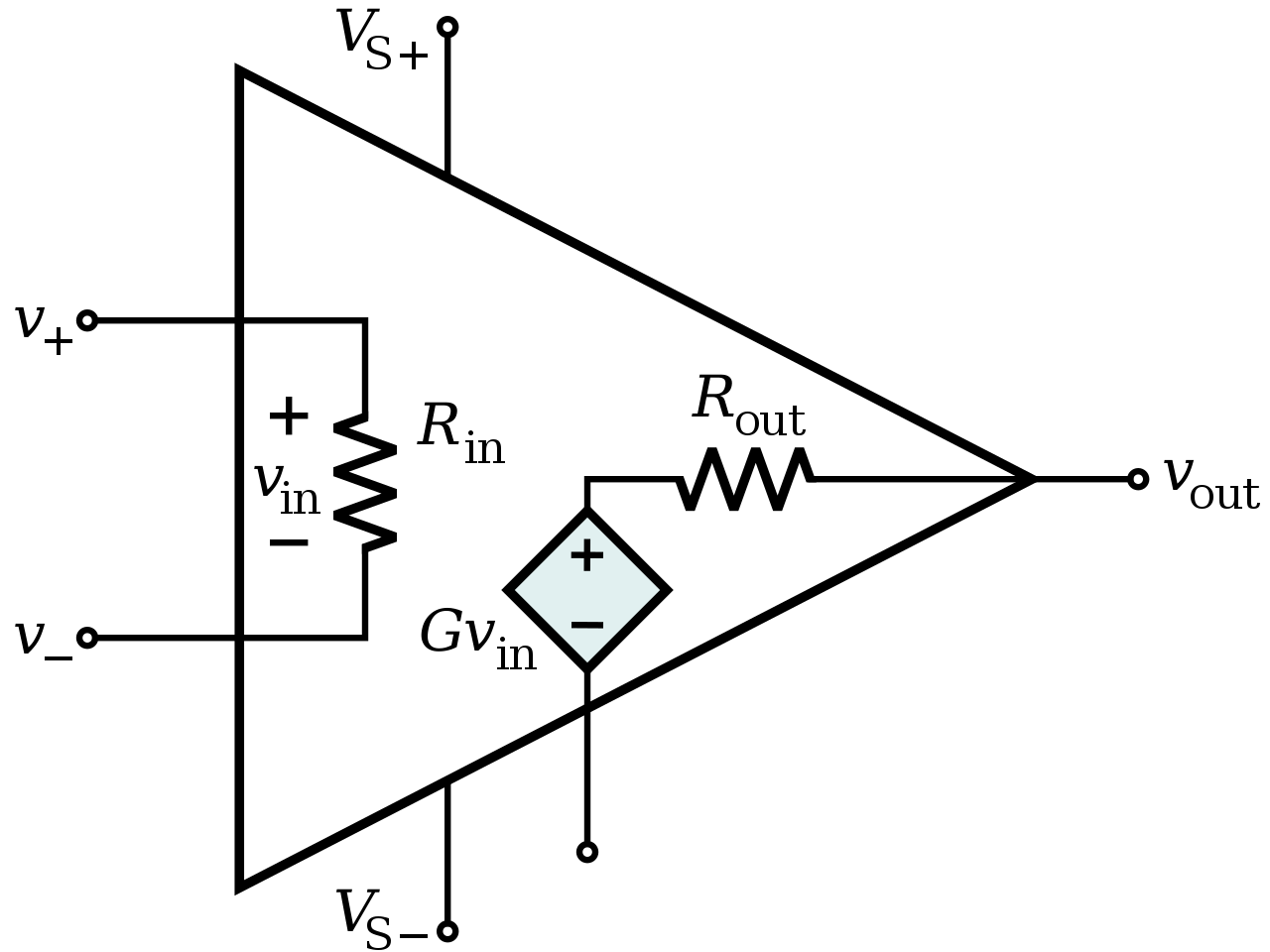

대망의 마지막 단계, 등가회로입니다.

사진은 복잡한 OP AMP 내부를 아주아주 단순하게 표현한 것입니다.

Saturation이고 뭐고 증폭의 기능에만 집중하여 표현된 것이기 때문에 Bias Voltage에 대한 것은 무시하셔도 됩니다.

사실 처음 볼 때는 굉장히 당황스럽습니다. 회로가 이어져있지도 않고 불친절하거든요. ^^;

얼핏 보면 이걸 어떻게 해석해야하나 막막하지만… 어렵게 생각하면 지는겁니다.

알고 보면 정말 쉬운 이 회로가 무엇을 의미하는지 차근차근 알려드리겠습니다. ㅎㅎ

우선 동작 과정은 아래와 같습니다.

1. 두 입력 단자의 전압차이만큼의 전압 \mathrm{{V}_{in}}이 입력저항 \mathrm{{R}_{in}}에 걸린다.

2. 무언가의 원리로 Gain 배 증폭된 입력전압 \mathrm{G{V}_{in}}이 출력단자로 나간다.

3. 증폭된 전압이 출력단자로 나가는 과정에서 출력저항 \mathrm{{R}_{out}}으로 인한 전압 강하가 발생하게되고 그만큼 감소된 전압이 출력전압 \mathrm{{V}_{out}}이 된다.

회로가 이어져있고 안 이어져있고는 신경쓰지 마시기 바랍니다. 신경쓰면 오히려 헷갈리기만 할 뿐입니다.

그냥 있는 그대로 입력저항에 전압이 걸리고 무언가의 원리로 증폭된 전압이 종속전압원에서 나온다라는 사실에만 주목하시면 됩니다.

입력과 출력 사이의 증폭 과정을 종속전압원 하나로 퉁쳐버렸기 때문에 사이에 연결이 없을 수 있는 것입니다.

여기서 눈여겨볼 것은 입력저항에 걸리는 전압을 입력전압으로 인식하여 증폭시킨다는 것입니다.

정확한 동작을 위해서는 두 입력단자 사이의 전압이 완전히, 모두 입력저항 \mathrm{{R}_{in}}에 걸려야합니다.

따라서 일반적으로 입력저항 \mathrm{{R}_{in}}은 주변의 다른 저항에 영향을 받지 않도록 큰 저항값을 가집니다.

때문에 이상적인(Ideal) OP AMP에는 ∞의 입력저항값을 가진다는 조건이 붙습니다.

출력저항 \mathrm{{R}_{out}}의 경우에는 반대가 됩니다.

증폭된 전압 \mathrm{G{V}_{in}}이 출력저항 \mathrm{{R}_{out}}을 지나면서 일어나는 전압 강하를 최소화해야하기 때문에 일반적으로 매우 작은 크기의 저항값을 갖습니다.

역시 이상적인(Ideal) OP AMP는 0의 출력저항값, 즉 출력저항이 없다는 조건이 붙게됩니다.

이게 OP AMP 등가회로의 전부입니다. 어때요? 별거 없죠? ^^

마치며…

이렇게 OP AMP의 첫 번째 강의가 끝났습니다.

이번 글에서 다룬 내용은 기초중의 기초로, 첫 단추가 중요하다는 말이 있듯이 최대한 기본 원리 이해에 중점을 두었습니다.

전체적인 내용을 한 문장으로 정리해보면 ‘OP AMP는 무엇인가’ 정도가 되겠네요.^^

중간중간 Ideal OP AMP니 뭐니 알 수 없는 단어들이 종종 튀어나왔을텐데요, 다음 글에서는 그런 것들을 다루려고 합니다.

가능하다면 하나의 글 안에 OP AMP의 모든 것을 정리하고 싶었는데 막상 시작해보니 내용이 너무 방대하네요… ㅎㅎ;

긴 글 읽어주셔서 감사드리고, 부디 오늘 배운 것들이 앞날에 도움되셨으면 좋겠습니다.

지금까지 공대생의 오아시스였습니다. ^^

이해하는데 정말 도움 됐어요 감사합니다 ^^

실험 구성하는 정도의 지식만 있으면 되는 저에게 정말 편한 설명입니다. 시리즈 설명 잘 보겠습니다

thank you

thank you

진짜 설명 잘하십니다.

정말 감사합니다ㅠㅠㅠ 전공책 보는데 이해 하나도 안되어 힘들었는데 ㅠㅠㅠㅠㅠ 저에게 정말 달콤한 오아시스입니다!!!

정말 훌륭한 글이네요.

3번 마지막 단락즈음에

“VCC와 VEE의 중간값을 기준으로 조금이라도 크면 VCC를, 조금이라도 작으면 VEE를 출력합니다.”

되어 있는데 V+와 V-의 중간값이 맞는것 아닌가요?

같은 말입니다

포스팅해도 되나요?

포스팅해도 되나요?

와~정말 쉽군요 ㅎ

OPAMP가 뭔지 조금 알겠네요…감사합니다.

이해가 쏙쏙 되는 친절한 강의 감사합니다!

학교에서 수업듣다 한참 헤매고 있었는데 많은 도움되었습니다 감사합니다!

내용이 상당히 도움되었습니다. Op-Amp circuit에서 Negative feeback을 사용하는 이유가 잘 이해가 되지 않았는데, 간단한 설명을 통해서, 실마리를 찾게 되고, 추가적인 자료 검색을 통해 결국 이해 했네요.

도움이 됐습니다. 감사합니다.